cyphen156

1장 논리 : Boolean 본문

Boolean : Base of Computer

불리언이란 뭘까?

간단히 말하면 On/Off기능을 가지고 있는 스위치다.

디지털 기기는 참과 거짓이라는 2진 논리로 모든 것들을 처리하는데 이 2진 논리를 응용해서 만든게 불리언(부울 논)다.

이 챕터에서는 부울 논리에 대해 공부하고, NAND 논리 게이트를 이용해 16비트 AND, OR, NOT, XOR 게이트와 멀티플렉서, 디멀티플렉서를 만들어 보고, 32비트 체계로 확장하는 것을 할 것이다.

부울 대수(Boolean algebra)

0/1로 표현되는 2진수 논리

기본 부울 연산자

- AND : A * B, A ∧ B

- OR : A + B, A ∨ B

- NOT : !A, ~A, ¬A

복합 부울 연산자

- NAND(NOT AND) : !(A ∧ B), 유니버셜 게이트

- NOR(NOT OR) : !(A ∨ B)

- XOR(EXCLUSIVE OR) : A ⊕ B

기본적으로 복합 부울연산자는 기본 부울 연산자의 조합이다.

그런데 특이하게 컴퓨터 논리 회로의 경우 복합부울연산자인 NAND게이트는 NOT게이트와 AND게이트의 조합인데 NAND게이트가 기본 게이트가 되어 다른 게이트들을 구현한다.

왜 거꾸로 NAND게이트로 NOT게이트와 AND게이트를 구현하는걸까?

실제 하드웨어를 만들때 트랜지스터를 가장 효율적으로 사용할 수 있는 구조를 가지고 있기 때문이라고 한다.

구현하는데 필요한 트랜지스터 수가 적으니 적은 공간을 차지하고, 저전력으로 동작하며, 여러 과정을 거치지 않아 빠른 계산속도를 낼 수 있게 한다고 한다.

부울 함수

진리표와 부울 표현식

어떤 부울 함수에 대해 진리표 또는 표현식이 있다면, 항상 표현식 또는 진리표를 만들어 낼 수 있다.

하지만 어떤 부울 함수에 대한 진리표의 표현은 유일(Unique)하지만, 부울 표현식은 여러 가지로 표현할 수 있으며, 더 짧고 간결하게 표현할 수 있다 == 단순화(최적화)할 수 있다.

논리 게이트

앞에서 부울 연산자는 기본연산자와 복합 부울 연산자가 있다고 했다.

이 부울 연산자를 표현해주는 것이 논리 게이트다!.

논리 게이트는 회로를 입력-출력의 형태로 표현하고, 기본 게이트(AND, OR, NOT), 조합(복합) 게이트(NAND, NOR, XOR ...)가 있다. 연산자와 다른 것은 조합 게이트는 입력값이 2개 이상일 때 사용되기 때문에 3입력 1출력 과 같은 복잡한 수식을 표현해낼 수 있다는 것이다.

하드웨어 기술 언어(Hardware Description Language)

하드웨어를 직접 만들어 테스트하는 대신 시뮬레이터를 통해 엄격한 테스트를 거쳐 가상으로 테스팅하는 하기 위해 설계된 소프트웨어

| HDL 프로그램(Xor.hdl) | 테스트 스크립트(Xor.tst) | 출력 파일(Xor.out) |

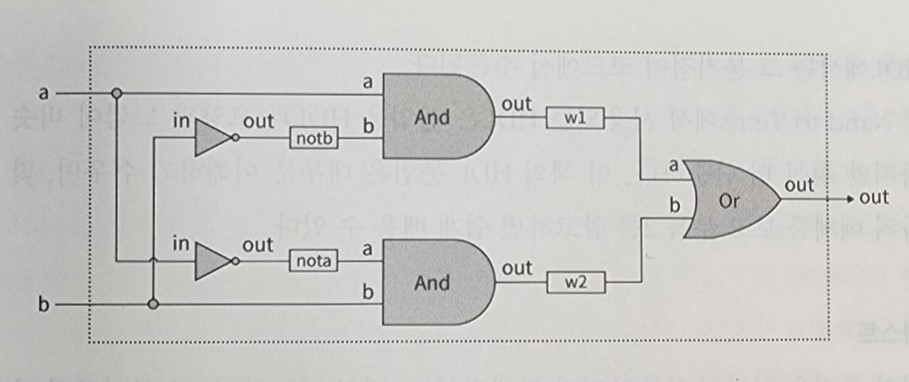

| Chip Xor { //header부분 입출력 IN a, b; OUT out; PARTS: //statement(); Not(in=a, out=nota); Not(in=b, out=notb); And(a=a, b=notb, out=w1); And(a=nota, b=b, out=w2); Or(a=w1, b=w2, out=out); } |

load Xor.hdl, output-list a, b, out; set a = 0, set b = 0, eval, output; set a = 0, set b = 1, eval, output; set a 1, set b 0, eval, output; set a = 1, set b = 1, eval, output; |

a | b | out ------------ 0 | 0 | 0 0 | 1 | 1 1 | 0 | 1 1 | 1 | 0 |

처음 봤을때는 무슨 소린지 잘 모르겠다. 천천히 뜯어보자

Chip Xor{ ... }칩 XOR에 대한 설계 파일이다.

IN a, b;

OUT out;HDL 헤더부분에는 a와 b라는 입력단자와 out이라는 출력단자가 있다는 것을 명시해주고 있다.

PARTS:

//statement();

Not(in=a, out=nota);

Not(in=b, out=notb);

And(a=a, b=notb, out=w1);

And(a=nota, b=b, out=w2);

Or(a=w1, b=w2, out=out);실제 회로도에 사용되는 논리 게이트들에 대한 입출력을 표시하고 있다.

구문이 곧 게이트 하나라고 보면 될 것 같다.

멀티플렉서 / 디멀티플렉서

서로 정반대의 기능을 하는 논리게이트

멀티플렉서는 3-입력 게이트로 2개의 입력 데이터비트(a와 b)와 1선택 비트를 통해 어떤 값을 출력할지 선택하는 게이트, 셀렉터라고도 한다.

디멀티플렉서는 반대로 한개의 입력 데이터와 선택 비트를 통해 a와 b라는 출력을 내보낸다.

다음으로 나오는 내용들은 구현에 대한 내용인데 이것은 프로젝트를 통해 진행하려 한다.

논리 회로에 대한 자세한 내용은 디지털 논리 회에서 다루겠습니다.

'수학/디지털 논리 회로' 카테고리의 글 목록 (tistory.com)

'수학/디지털 논리 회로' 카테고리의 글 목록

Cyphen의 개인 공부 블로그입니다. 프사는 아는 동생이 그려준 그림 주인장과 싱크로율 0%

cyphen156.tistory.com

//모든 자료들은 Nand2Tetris홈페이지에서 찾을 수 있습니다.

또는 cyphen156/Work-space: Studying (github.com)에서 찾으실 수 있습니다.

'프로젝트 > Nand2Tetris' 카테고리의 다른 글

| 3장 메모리 : 모든것은 결국 기억장치 관리다 (0) | 2023.07.10 |

|---|---|

| 2장 프로젝트 : 가산기 (0) | 2023.07.07 |

| 2장 논리 연산 (0) | 2023.07.07 |

| 1장 프로젝트 (0) | 2023.07.07 |

| 컴퓨팅 시스템 구현하기 : Bottom Up (0) | 2023.06.27 |